이번 포스트에서는 실습에 사용하기 좋은 다양한 회로도를 소개하겠습니다.

주어진 2bit 크기의 2진수 2개를 더하는 회로도(반가산기, 전가산기 사용)

반가산기 (Half Adder)

반가산기는 두 개의 이진수 입력 A와 B의 합을 계산하는 논리회로입니다. 반가산기는 두 개의 출력, 즉 합(Sum)과 자리올림수(Carry)를 생성합니다.

$Sum: S = A \oplus B$

$Carry: C = A \cdot B$

여기서 $\oplus$는 배타적 논리합(XOR) 연산을 나타내고, $\cdot$는 논리곱(AND) 연산을 나타냅니다.

전가산기 (Full Adder)

전가산기는 세 개의 이진수 입력 A, B 그리고 자리올림수 입력 C_{in}을 받아서 이들의 합을 계산하는 논리회로입니다. 전가산기 역시 두 개의 출력, 즉 합(Sum)과 자리올림수(Carry)를 생성합니다.

$Sum: S = A \oplus B \oplus C_{in}$

$Carry: C_{out} = (A \cdot B) + (B \cdot C_{in}) + (C_{in} \cdot A)$

여기서 +는 논리합(OR) 연산을 나타냅니다. 전가산기는 두 개의 반가산기와 하나의 OR 게이트로 구성될 수 있습니다.

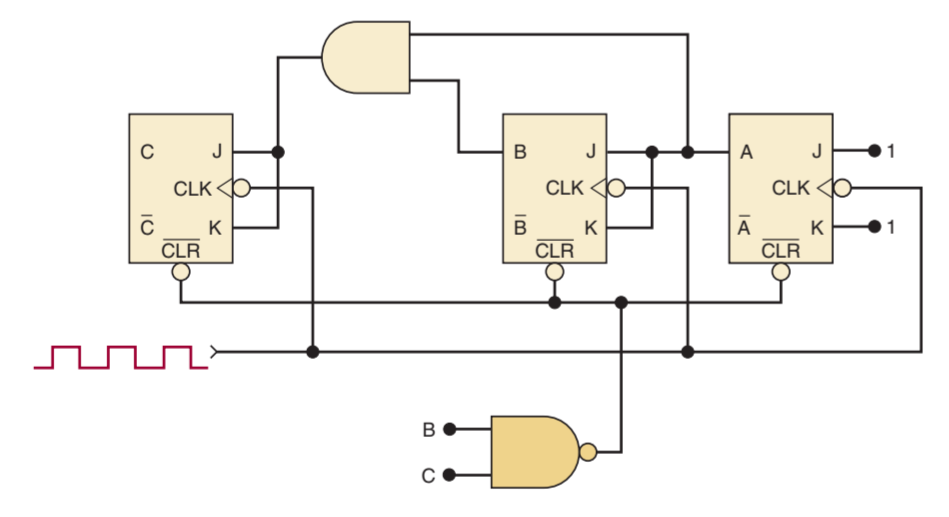

MOD - 10 카운터

MOD-10 카운터는 0부터 9까지 총 10개의 상태를 가지며, 10진수를 카운트하는 카운터입니다. J-K 플립플롭은 카운터의 기본 구성 요소로 사용되며, 각 플립플롭은 비트 단위로 상태를 나타냅니다. MOD-10 카운터를 구성하기 위해서는 4개의 J-K 플립플롭이 필요합니다. 이 4개의 플립플롭은 2진수 4비트를 사용하여 0에서 9까지의 상태를 나타내며, 10번째 상태(1010)에서 초기 상태(0000)로 리셋됩니다.

J-K 플립플롭의 입력은 J와 K이며, 두 입력이 모두 HIGH일 때 플립플롭의 출력은 토글(toggle)됩니다. 따라서, 카운터의 특정 상태에서 플립플롭의 상태를 변경하거나 리셋하기 위해 적절한 J-K 입력을 설계해야 합니다. MOD-10 카운터에서는 플립플롭의 출력이 '1010'이 될 때, 모든 플립플롭을 '0000'으로 리셋하는 동작을 수행합니다. 이러한 리셋 동작을 통해 카운터는 0부터 9까지 순차적으로 카운트한 후 다시 0으로 돌아가게 됩니다.

설계 과정에서는 플립플롭의 이전 상태와 다음 상태를 고려하여 J와 K 입력을 결정하며, 이 입력은 각 플립플롭의 클록 펄스에 따라 변화합니다. 이러한 구성으로 J-K 플립플롭을 이용한 MOD-10 카운터가 구현됩니다.

MOD - 6 카운터

스톱워치 (계수 범위 0~59)

위에서 주어진 MOD - 10 카운터에서 Z2 칩의 3번 핀 출력을 클럭으로 갖는 MOD - 6 카운터는 계수범위가 0에서 59까지를 갖는다.

스톱워치의 일시정지 기능을 구현하고자 한다면, MOD - 10에 전달되는 파형을 AND 게이트를 통해 ENABLE / DISABLE하면 된다.

아래는 MOD - 10 카운터에 스위치를 통한 ENABLE / DISABLE을 구현한 회로도이다.(MOD-6 카운터 생략)

'전기 · 전자 · 회로 > 디지털 공학' 카테고리의 다른 글

| 디지털 공학 9화 - 7 세그먼트 디코더, 캐소드와 애노드 (0) | 2024.08.08 |

|---|---|

| 디지털 공학 7화 - 동기/비동기 카운터 (0) | 2024.08.07 |

| 디지털 공학 6화 - 조합 논리 회로 분석 및 구현 예제 (1) | 2024.08.07 |

| 디지털 공학 5화 - 주관식/객관식 문제 해설 (0) | 2024.08.07 |

| 디지털 공학 4화 - 대안 표시, EN/DISABLE, TTL, 간단한 실습 (0) | 2024.08.07 |