Synchronous/ASynchronous counter

74LS76 datasheet

동기/비동기 카운터는 플립 플롭을 이용하여 구현합니다. 이번 예제에서 사용될 플립플롭인 J-K 플립 플롭에 대하여 설명하겠습니다.

아래는 J-K 플립 플롭의 동작표(Function Table)입니다.

플립 플롭이 HIGH 또는 1 상태가 되도록 하면 세트라고 하며, LOW 또는 0 상태가 되도록 하면 CLEAR 또는 RESET 상태라고 합니다. (동작표 내의 X 표시는 Don't Care 또는 DC라고 하며, 해당 위치의 값이 0이든 1이든 상관없이 출력 또는 동작이 일어납니다)

J = K = 1 = Preset = Clear일 때, NGT(Negative-Going Transition)에서 상태가 반전(TOGGLE) 됩니다.

NGT에서 반응할지, PGT에서 반응할지는 설계 사양에 따라 다릅니다.

비동기식(리플) 카운터

J-K 플립 플롭을 이용하여 비동기식 카운터(리플 카운터)를 만드는 예제입니다.

아래 회로와 타이밍 다이어그램을 확인하고 직접 구현해 봅니다. (74LS76)

리플 카운터에서의 전파 지연

리플 카운터는 계수 동작을 하기 위해 최소한의 회로 소자로 구성할 수 있기 때문에 가장 간단한 2진 카운터의 형태이다.

그러나 각각의 플립플롭은 앞 단의 플립플롭의 출력 값이 변화할 때 동작할 수 밖에 없으므로 한가지 단점을 갖는다. 이를 자세히 살펴보면, 각각의 플립플롭은 고유의 전파지연시간($t_{pd}$)이 있어서 출력 펄스가 인가되더라도 출력이 바로 나오지 않고 $t_{pd}$만큼의 시간이 경과된 이후에 나오게 된다.

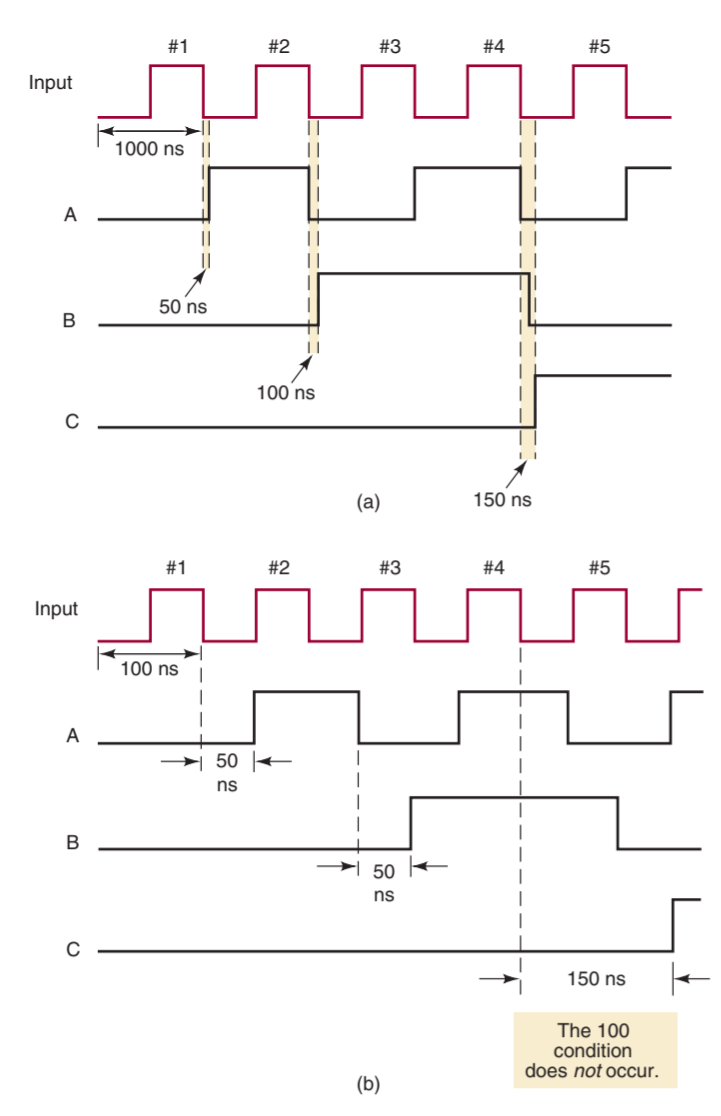

아래 주어진 3비트 리플 카운터를 예로 들어 보겠다.

(a) 타이밍 다이어그램은 입력 펄스가 1000ns (클럭 주기 T = 1000ns)마다 발생하는 것을 보이며, 각각의 플립플롭은 50ns 의 전파 지연을 갖는다고 가정한다($t_{pd}$ = 50ns). A 플립플롭의 출력은 입력 펄스의 하강 천이(NGT) 후 50ns 후에 반전된다. 마찬가지로 B는 A가 1에서 0으로 변한 후, 50ns 이후에 변환하고, B가 1에서 0으로 변한 후, 50ns 이후에 C가 반전된다. 결과적으로 입력 클럭 펄스의 4번째 하강 천이가 발생할 때, 출력 C는 150ns의 지연이 있은 후에 HIGH가 된다. 이런 경우는 전파 지연 시간이 클럭 주기에 비해 작기에 문제가 없다.

하지만 (b) 타이밍 다이어그램을 살펴보겠다. (b)의 파형은 입력 펄스가 100ns마다 한 번씩 발생하는 경우를 보인다. 각 플립플롭의 출력은 CLK 입력이 1에서 0으로 변한 후 50ns 이후에 변한다.

4번째 입력 펄스의 하강시점 이후를 자세히 살펴보자. 4번째 입력 펄스가 하강한 후, 150ns가 지나서 C출력은 HIGH로 되었다. 그런데 이 사이에 5번째 입력 펄스가 들어와서 A출력은 HIGH로 바뀐다. 이런 상황으로 인해 $C=1,\ B = A = 0$ 인 상태는 만들어 질 수 없다(계수 100). 그러므로 제대로 된 2진 카운터가 아니다.

결론적으로, 클럭 주기 $T_{CLOCK}$, 플립플롭의 개수 $N$, 전파지연시간 $t_{pd}$ 일 때 아래 조건을 만족하여야 한다. (참고 : 주기 $t$, 주파수 $f$ 일때, $t = 1 / f$)

$T_{CLOCK} ≥ N\times t_{pd}$

$f_{max}=\frac{1}{N\times t_{pd}}$

예를 들어, 74LS112 J-K 플립플롭을 이용한 4비트 리플 카운터를 구현하는 경우를 고려해보겠다.

74LS112의 경우 $t_{PLH}$ = 16ns, $t_{PHL}$ = 24ns 이다. $f_{max}$를 구하기 위해 값이 더 큰 쪽을 기준으로 하겠다. 즉, $t_{pd} = t_{PHL} = 24ns$ 로 하겠다.

$f_{max} = \frac{1}{4\times 24ns} = 10.4MHz$

카운터 비트 수가 증가함에 따라 총 전파 지연 시간은 증가하므로 $f_{max}$의 값은 감소할 수 밖에 없다.

비동기식 카운터는 매우 높은 주파수에는 적절치 않으며, 많은 비트 수를 갖는 카운터에는 사용이 어렵다는 특징을 확인할 수 있다.

동기식(parallel) 카운터

리플 카운터의 문제점은 플립플롭의 전파 지연(PD)이 누적된다는 것이다. 즉, 플립플롭에서 모든 상태가 입력 펄스에 동기되어 동시 변화가 이루어지지 않는다는 것이다.

이것을 해결하기 위해 모든 플립플롭이 입력 클럭 펄스에 의해 동시에(병렬로) 트리거되는 동기식 카운터(synchronous counter) 또는 병렬 카운터(parallel counter)를 사용함으로써 해결할 수 있다.

동기식 카운터를 구성하는 기본적인 원리는 다음과 같다.

임의의 플립플롭에 대해서 하위 단의 플립플롭 출력이 모두 HIGH일 때에만 그 플립플롭의 J와 K입력이 HIGH 상태가 되도록 연결해야한다.

모든 플립플롭에 입력 펄스가 인가되기 때문에, 각 플립플롭이 입력 클럭 펄스에 의하여 반전되거나 현 상태를 유지할 수 있도록 하는 회로가 추가되어야 한다. 이는 J, K 입력을 이용하여 처리될 수 있으며, 다음 이미지를 참고하라.

계수 순서를 진리표로 나타내면 다음과 같다.

Shift register

데이터의 직렬 전송 동작의 기본이 되는 시프트 레지스터이다.

시프트 레지스터는 플립플롭에 저장된 2진수를 매 클럭마다 하나의 플립플롭에서 다른 플립플롭으로 이동하도록 결선된 플립플롭의 집합이다.

전자 계산기에서 화면의 숫자가 새로운 숫자의 단추를 누를 때마다 옆으로 이동되는데 이와 같은 동작이 시프트 레지스터에서 일어난다.

J, K 입력이 CLK 천이와 거의 같은 시간에 변하는 경우가 있기에 플립플롭들은 매우 작은 홀드 시간을 가질 필요가 있다. CLK에서 출력까지의 전파 지연보다 작은 $t_H$값을 갖는 에지 트리거 플립플롭을 사용하여 구현한다.

Serial

Serial은 일반적으로 데이터를 한 비트씩 순차적으로 전송하는 방식을 의미합니다. 이는 병렬 전송과 반대되는 개념입니다. 위에서 설명한 Shift register도 포함됩니다.

Serial 통신의 장점

- 배선 간소화: 병렬 전송에 비해 배선이 적어 연결이 단순하고 설치 비용이 절감됩니다.

- 노이즈 저항성: 장거리 전송 시 노이즈에 대한 저항성이 높습니다.

순차 논리 회로 구현 예제 (MOD 수가 $2^N$보다 작은 카운터)

플립플롭을 3개 사용하여 $2^3$까지 계수하는 MOD-8 카운터를 MOD-6 카운터로 만들고자 한다.

- MOD-8 카운터가 110 전까지 계수하여야 한다.

- MSB가 C, LSB가 A, 나머지 하나가 B라고 하였을 때, C = B = 1 이면서 A = 0 일때, C = B = A = 0 상태로 CLEAR하여야 한다.

- C = B = 1 이면 A 값에 상관없이(DON’T CARE, 무정의 조건) 초기화(CLEAR)할 필요가 있다.

- 이를 회로로 구현한다.

더 많은 예제를 확인하고 싶다면

다음 포스트를 확인해주세요 !

'전기 · 전자 · 회로 > 디지털 공학' 카테고리의 다른 글

| 디지털 공학 9화 - 7 세그먼트 디코더, 캐소드와 애노드 (0) | 2024.08.08 |

|---|---|

| 디지털 공학 8화 - 회로도 모음 (0) | 2024.08.08 |

| 디지털 공학 6화 - 조합 논리 회로 분석 및 구현 예제 (1) | 2024.08.07 |

| 디지털 공학 5화 - 주관식/객관식 문제 해설 (0) | 2024.08.07 |

| 디지털 공학 4화 - 대안 표시, EN/DISABLE, TTL, 간단한 실습 (0) | 2024.08.07 |